什么是背板?

背板可以用于将多个设备、模块或电路板连接在一起,实现高速数据传输、信号传输和控制功能。背板通常具有多个连接器,可以插入不同的模块或电路板,并通过高速信号线或光纤进行连接。

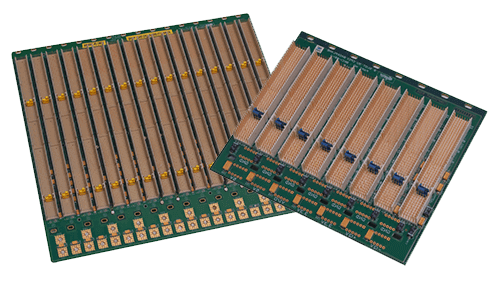

CompactPCI 背板

背板可以提供高带宽、低延迟、可靠的连接,广泛应用于通信设备、网络设备、服务器、计算机等领域。

考虑到背板要承受高频率、大容量的高速信号传输,因此背板PCB在设计时需要考虑到电气性能、机械性能、可靠性、散热性能等多个方面,在制造时需要使用高性能的材料,采用高精度的加工工艺,以保证背板PCB能够达到性能要求并且工作稳定。

背板的板材选型及叠构设计

背板的板材选型

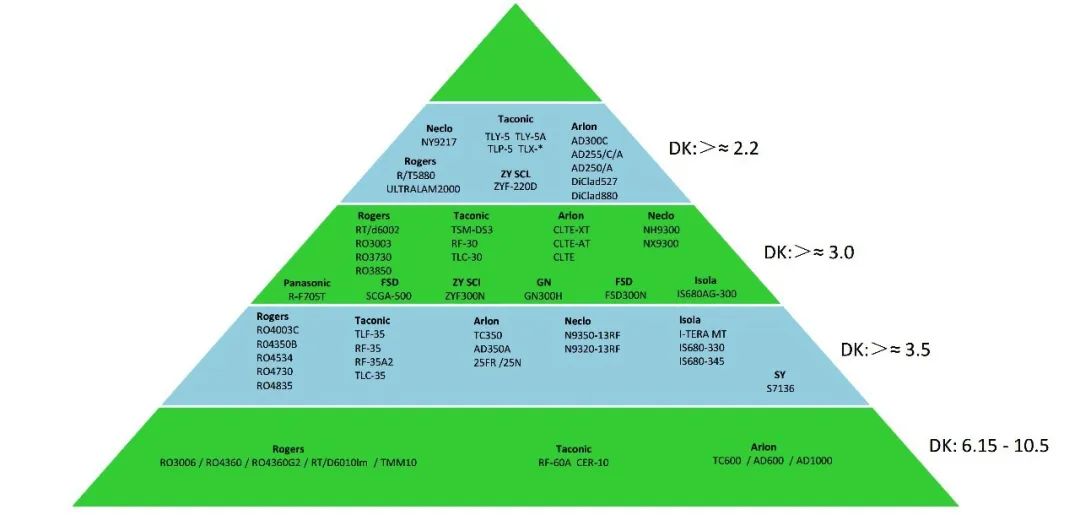

背板通常采用FR4-TG170级别以上的板材,与一般的FR4-TG130相比,玻璃态转化温度更高,耐燃性更好,通常选取介电常数ε(Dk)不大于4.4的板材,以减少信号间的串扰。

高速板材选型

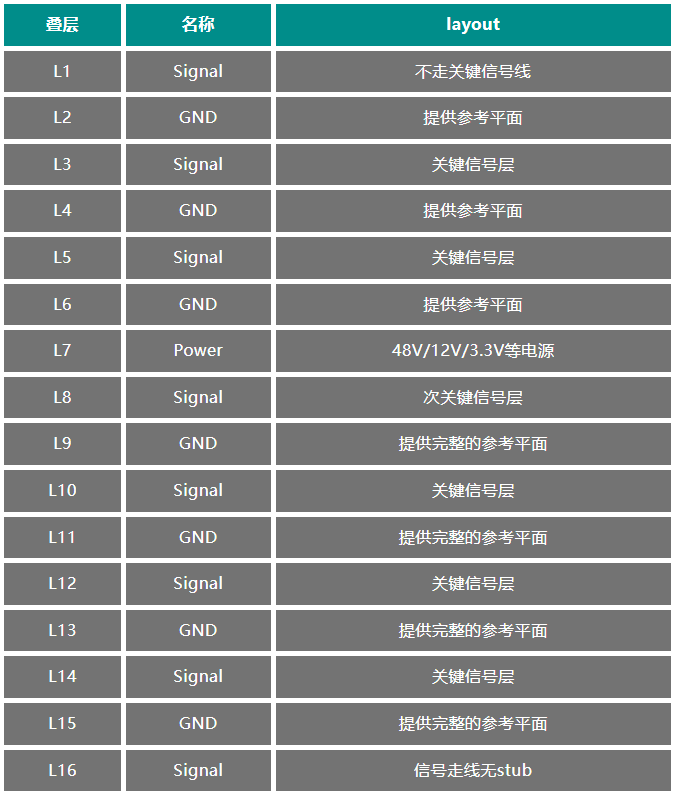

背板的叠层设计

大电流背板的叠层设计

有些背板除了需要考虑多种类型的型号线走线之外,还承载着给各个业务板卡供电的功能。比如OpenVPX 背板,需要承载多种电压的总电流高达100A。

此时需要使用多个电源平面来满足电流的需求,可以选择使用分段策略,在同一层内将电源平面与与高速信号线区域分开布线,如下图所示。

如果PCB的层数允许,使用地平面将各个电源层隔开,在保证信号线有良好参考平面的同时,能够保障整个PCB具有良好的屏蔽性。

背板的关键信号走线

背板存在3类信号线:时钟总线、管理总线和高速信号线。

时钟总线

时钟总线信号均为差分信号,如M-LVDS电平的多点低电压差分信号,可以使多个驱动器或接收器共享同一个物理链路,时钟总线设计遵循以下原则 :

时钟总线源端及末端就近摆放100Ω端接电阻,最大限度地吸收反射信号。

时钟总线的走线长度不能超过芯片的驱动能力。

时钟总线经过的过孔尽量不要超过 2 个,减少过孔带来的寄生电容,过孔附近就近打接地过孔,为交流信号提供最短的回流路径,每个过孔的出现都会使信号阻抗出现不连续的现象。

时钟总线间距需采取3W原则,最大程度地减少信号间的串扰。

总线的走线需伴随有完整的参考平面,保证总线信号回流路径最短,同时特征阻抗不会发生突变。

差分线的特征阻抗为100Ω。

管理总线

管理总线信号均为单端信号,物理接口形式为I2C,管理总线设计遵循以下原则:

管理总线源端及末端采用就近端接上拉4.7K电阻,提高总线的驱动能力并吸收一部分反射。

管理总线的走线长度不能超过芯片的驱动能力。

单端信号线的特征阻抗设计为65Ω。

高速信号线

高速信号线主要是业务板和交换板之间的数据交换总线和友邻业务板之间的数据总线,均为高速差分信号线,高速信号线遵循以下设计原则:

差分线经过的过孔尽量不要超过 2个,减少由过孔带来的寄生电容,并在过孔附近就近打接地过孔,为交流信号提供最短的回流路径。

差分线需和其他网络间距采取3W原则,最大程度减少串扰。

差分线的走线需伴随完整的参考平面,保证总线信号回流路径最短及特征阻抗不发生突变。

差分线对采用严格等长的走线方式,保证差分线对内信号时序稳定。

差分线的特征阻抗设计为100Ω。

随着电子封装、元件和系统向微型化、高密度的方向发展,数据传输速率的要求越来越高,连接器逐渐向微间距,多排插针,高密度的方向发展。普通的焊接型连接器已无法满足设计要求,逐渐被压接型连接器所替代。压接连接的失效率要比普通电烙铁焊接(无热冲击、热损伤)低一个数量级。

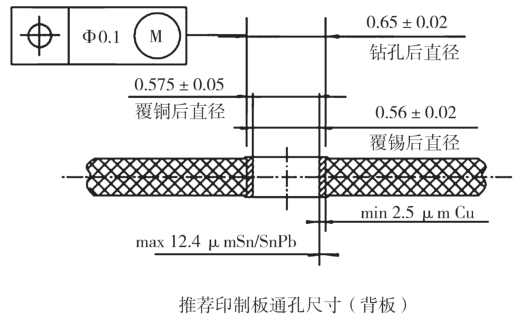

压接工艺是在常温下将柔性或硬性插针与印制板金属化孔配合而形成的一种连接,依靠金属之间的相互作用,在插针与金属化孔之间形成类似于原子熔融状态的紧密接触,实现连接器和印制板导线之间机械和电气连接。

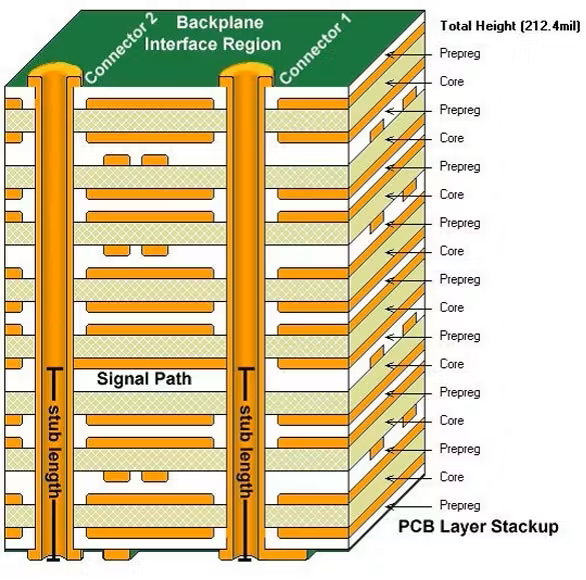

过孔背钻

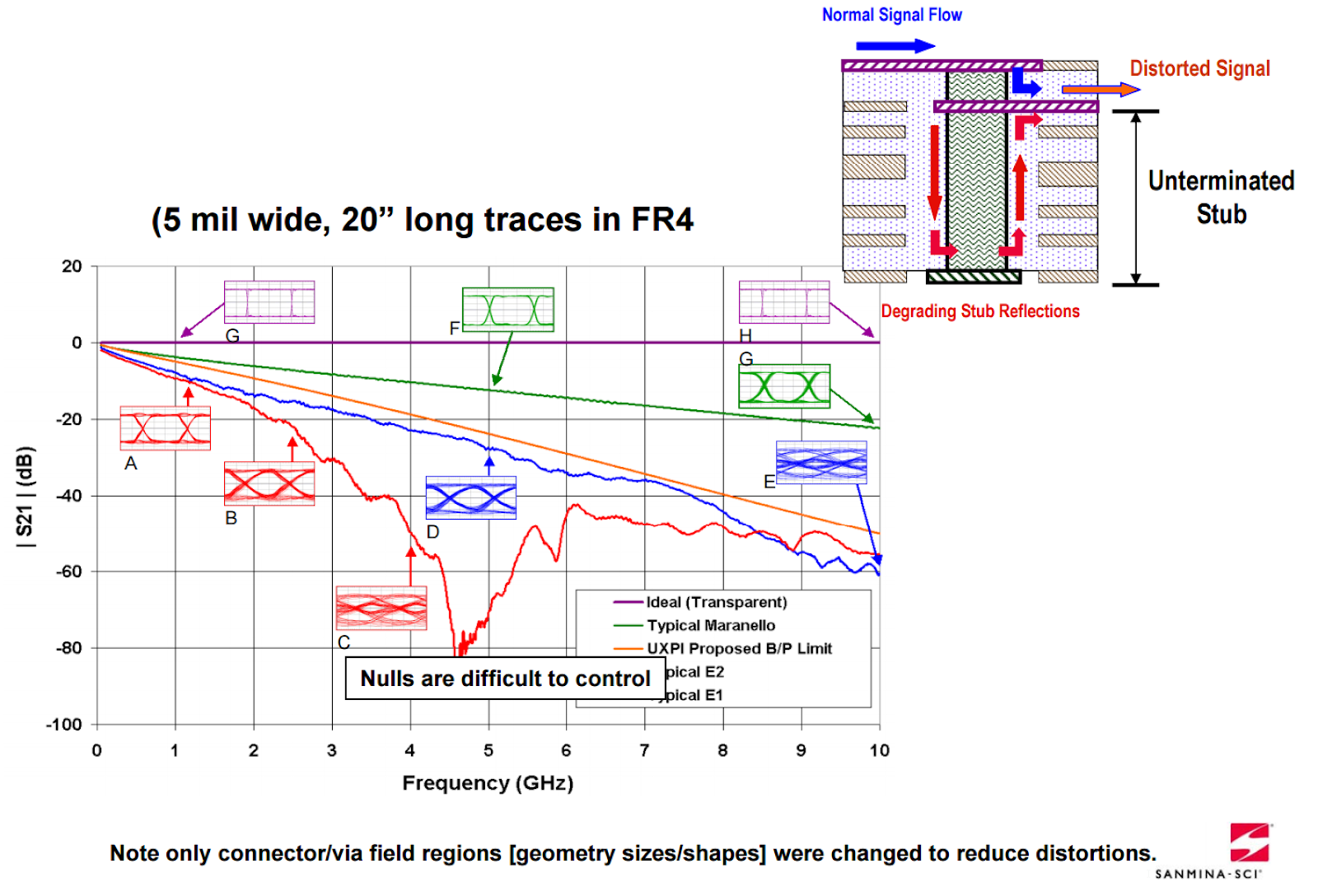

当我们设计好背板,在机箱里面和业务板跑业务测试出现速率跑不上去或者更严重的丢包问题时,我们往往会关注业务板与背板之间的连接器,导致阻抗不连续,出现信号完整性问题。但大多时候,阻抗的不连续实际源自过孔。

电镀通孔(PTH)会让给高速信号带来抖动、衰减,产生更高的误码率。信号速率越高,电镀通孔(PTH)带来的信号失真越大。PTH过孔在6.25Gb/s时的失真通常比在3.125Gb/s时产生的失真大两倍以上。

过孔残桩带来的信号失真

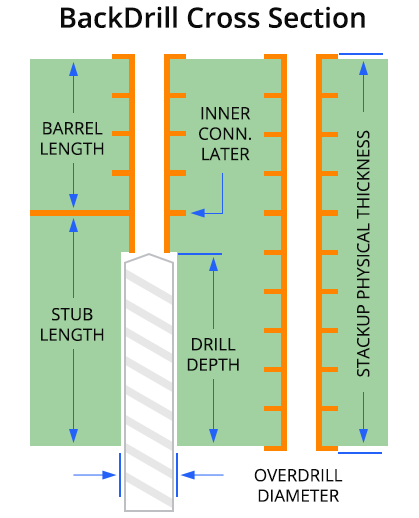

背钻已被广泛认为是把过孔对信号衰减降到最低程度简单而有效的方法。背钻又被称为定深钻孔,采用数控钻孔设备,通过清除过孔残段(Stub)。

背钻使用的钻头直径一般比过孔大大8mil,以便移除不需要的导体残段。为了保证背钻不会穿透附近的走线和平面,过孔附近的走线和平面到背钻孔对应层的间距应该在10mil以上。

背钻横截面示意图

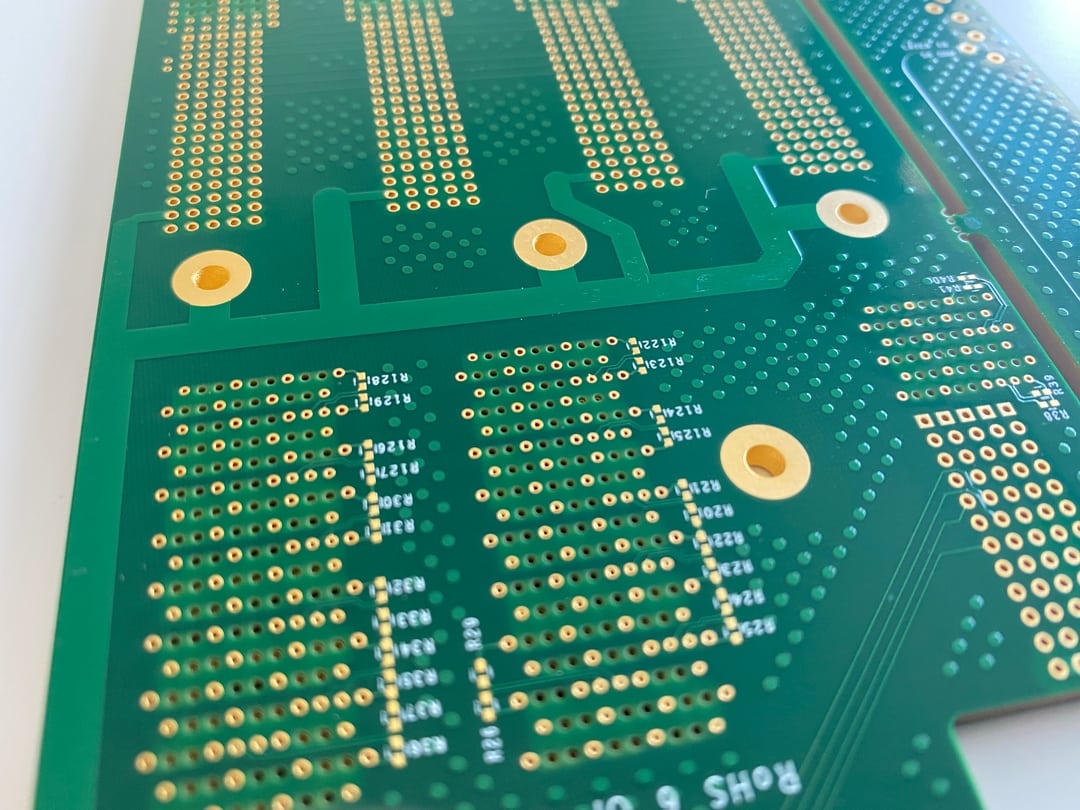

完成背钻的背板PCB-明阳电路